#### Northeastern Facilitating Spectrum Access by Noise Guessing University

Arslan Riaz<sup>1</sup>, Furkan Ercan<sup>1</sup>, Zeynep Ece Kizilates<sup>1</sup>, Akshaya Bali<sup>1</sup>, Alperen Yasar<sup>1</sup>, Kevin Galligan<sup>3</sup>, David Starobinski<sup>1</sup>, Ken R. Duffy<sup>4,</sup> Muriel Medard<sup>2</sup>, Rabia Tugce Yazicigil<sup>1</sup>

PI : Muriel Medard<sup>2</sup>, David Starobinski<sup>1</sup>, Rabia Tugce Yazicigil<sup>1</sup>

<sup>1</sup>Department of Electrical & Computer Engineering Boston University, Boston, MA, <sup>2</sup>Department of Electrical Engineering and Computer Science Massachusetts Institute of

Technology, Cambridge, MA, <sup>3</sup>Hamilton Institute, Maynooth University, Maynooth, Ireland,

<sup>4</sup>Department of Electrical and Computer Engineering & Department of Mathematics, Northeastern University, Boston, MA, USA

Award Numbers: 2128517 (https://www.nsf.gov/awardsearch/showAward?AWD\_ID=2128555 (https://www

## Motivation

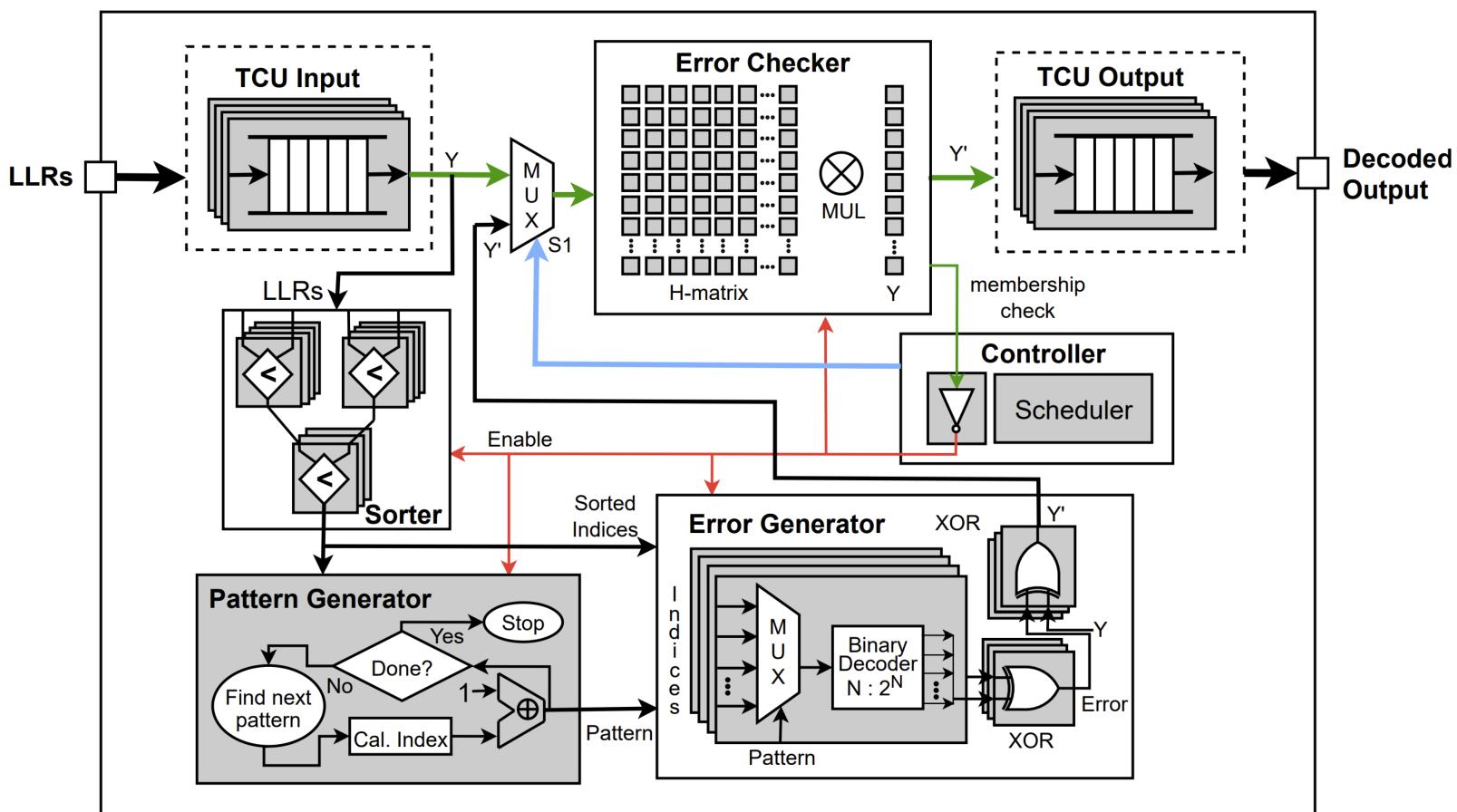

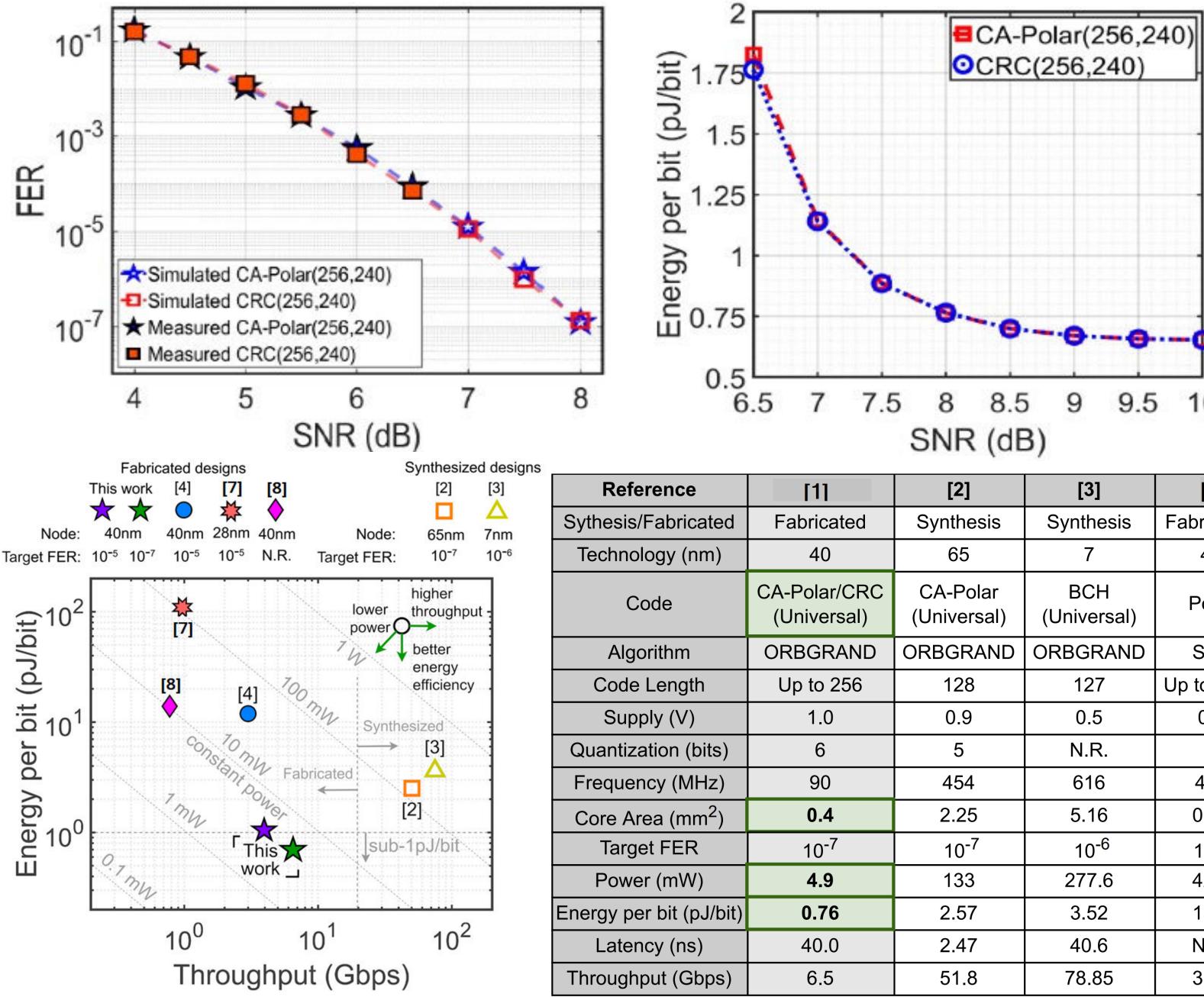

project investigates cross-layer optimization of This hardware, algorithms, and systems to address spectrum **†** utilization and sharing challenges, including energy efficiency and security. Toward this goal, we introduced the first soft-detection integrated universal decoder using ORBGRAND.

- Decode any short-length and high-rate codes

- At target FER  $10^{-7}$

- Ultra-low energy consumption of 0.76pJ/bit

- Lowest power consumption of 4.9mW

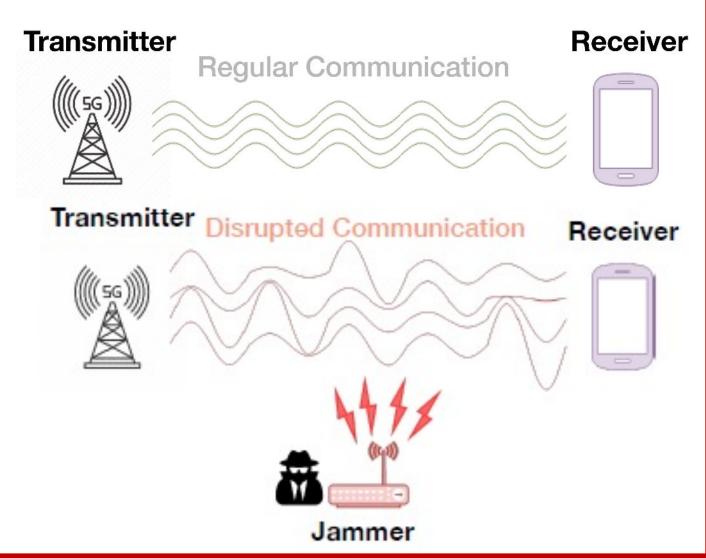

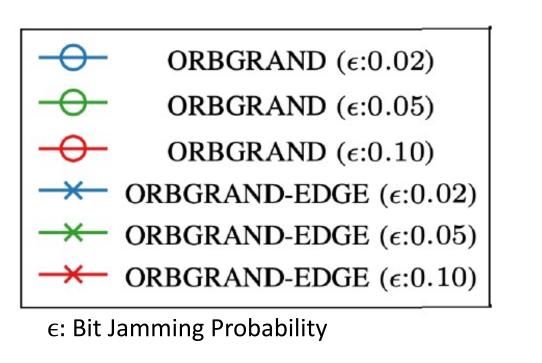

### **Interference and Jammers**

- Interference and jammers disrupt communication severely

- Channel signal strength indicators can easily detect anomalies but cannot help recover transmitted data

- Disruption causes re-transmission with overhead in latency and power consumption

- **GRAND-EDGE** resilience adds against jamming events

- Comparable throughput of 6.5Gbps

- Decoder performance is independent of the codebook

- Dynamically adapts to the channel noise conditions

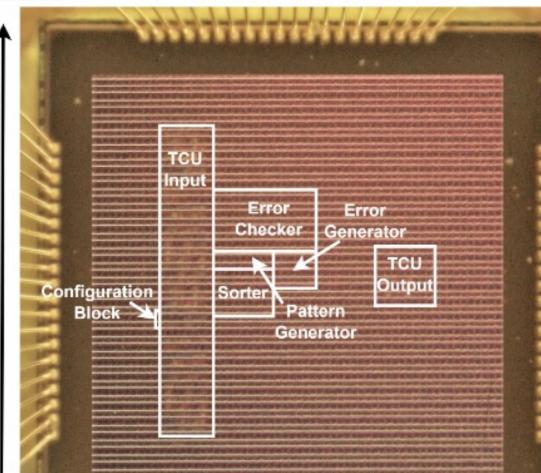

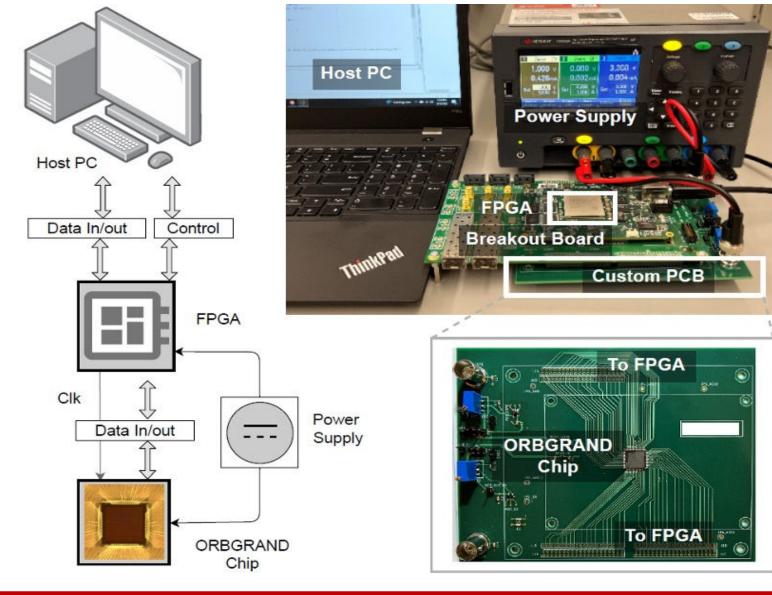

### **ORBGRAND Chip Architecture**

# 3 mm

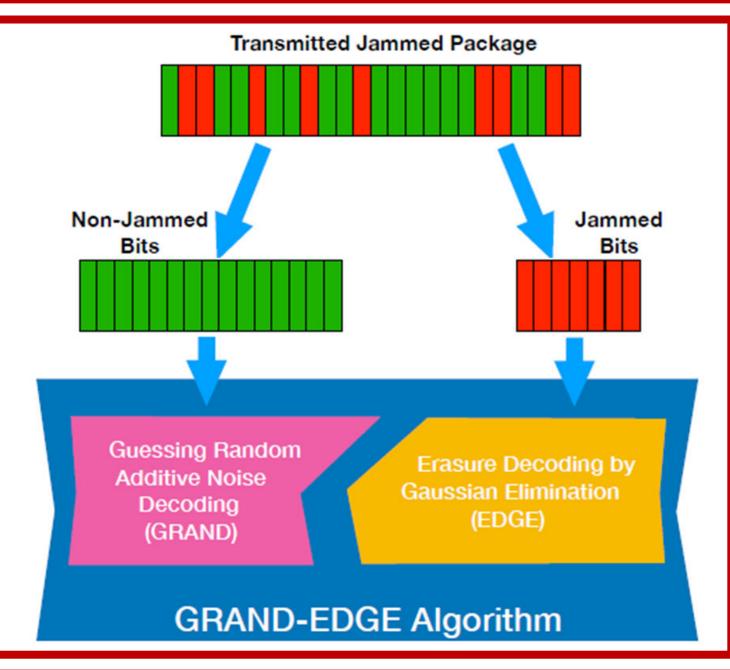

### **GRAND-EDGE** Algorithm

jamming-resilient algorithm We introduced a leveraging GRAND:

- **Step 1**: Identify and separate jammed bits from unjammed bits

- Step 2-GRAND: Perform error correction on unjammed bits

- Step 3-EDGE Subroutine: Estimate values of jammed bits through Gaussian Elimination

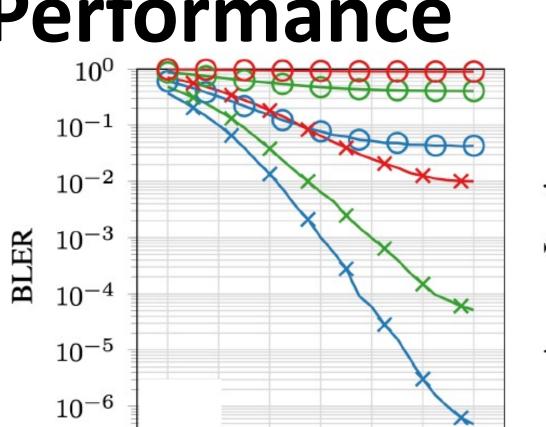

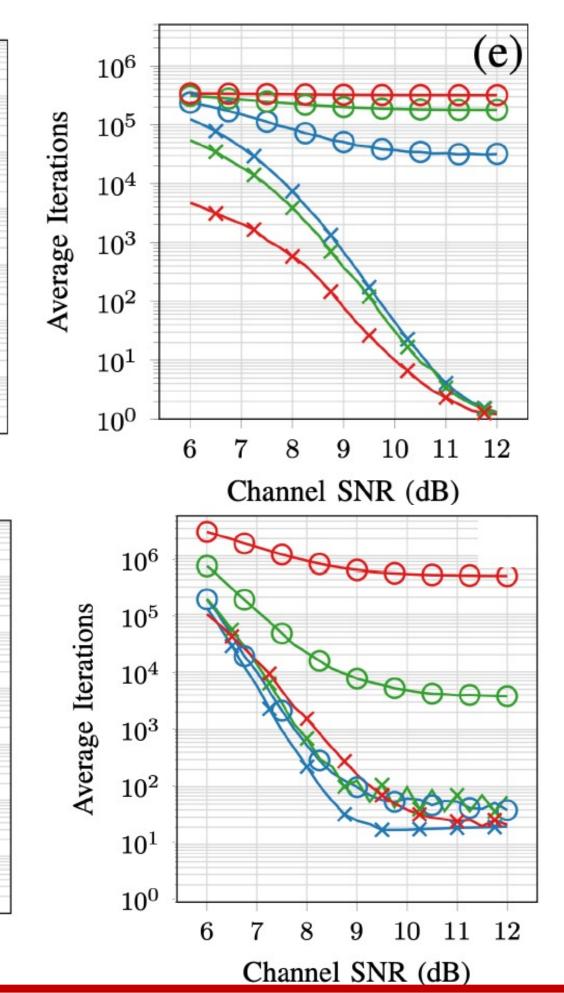

# **GRAND-EDGE** Performance

-0-GRAND ( $\epsilon$ :0.02) -0 GRAND ( $\epsilon$ :0.05) <del>-0</del>-GRAND ( $\epsilon$ :0.10)  $\rightarrow$  GRAND-EDGE ( $\epsilon$ :0.02)  $\rightarrow$  GRAND-EDGE ( $\epsilon$ :0.05)  $\rightarrow$  GRAND-EDGE ( $\epsilon$ :0.10)

**Hard-Detection Scenario**

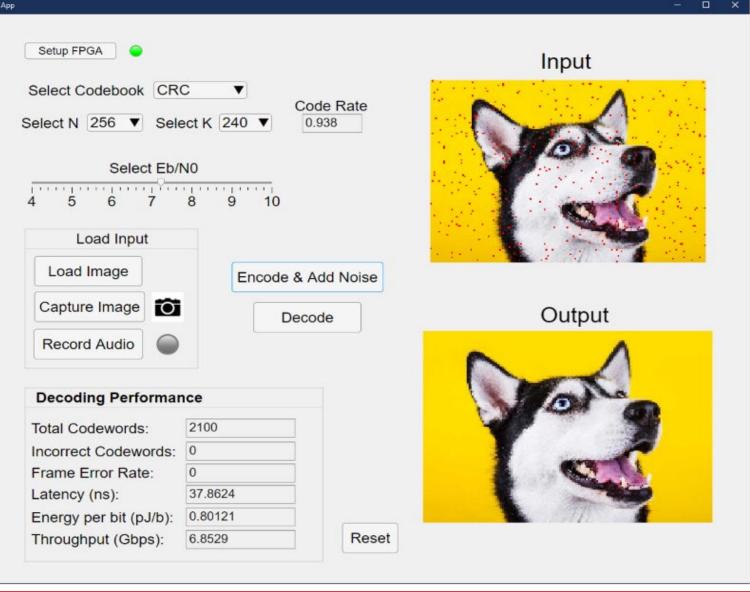

# Setup and GUI for the ORBGRAND Demo

### **ORBGRAND Chip Measurement Results**

#### **Soft-Detection Scenario**

Channel SNR (dB)

#### **Broader Impacts**

- Muriel Médard, Invited Speaker, "A Brief Tutorial on Guessing Random Additive Noise Decoding (GRAND)," 2023 IEEE ComSoc International School, Boston, June 2023

- M. Médard, Keynote Speaker, "Guessing Random Additive Noise Decoding (GRAND) or Universal Decoding Algorithm, and Relation to Signal Processing," IEEE LatinCom, Panama, November 2023

- M. Médard, Invited Speaker, "6G What to Know Now," European Patent Office, November 2023

- R. T. Yazicigil, MediaTek (Semiconductor Research Corporation Member Company), "Decode Any Code with GRAND", November 2023

- R. T. Yazicigil, Lockheed Martin, "Decode Any Code with GRAND", December 2023

- K. R. Duffy, M. Médard, Invited Speaker, "GRAND: Guessing Random Additive Noise Decoding," Centrale Supélec Université of Paris-Saclay Seminar Series, Virtual, February 2024

- K. R. Duffy, Invited Speaker, "Guessing Random Additive Noise Decoding", ECE Distinguished Seminar Series, University of Michigan, March 2024

| Reference[1][2][3][4]Sythesis/FabricatedFabricatedSynthesisSynthesisFabricatedTechnology (nm)4065740CodeCA-Polar/CRC<br>(Universal)CA-Polar<br>(Universal)BCH<br>(Universal)PolarAlgorithmORBGRANDORBGRANDORBGRANDSCLCode LengthUp to 256128127Up to 1024Supply (V)1.00.90.50.9Quantization (bits)65N.R.6Frequency (MHz)90454616430Core Area (mm²)0.42.255.160.64Target FER10 <sup>-7</sup> 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW)4.9133277.642.8Energy per bit (pJ/bit)0.762.573.5213.2Latency (ns)40.02.4740.6N.R.Throughput (Gbps)6.551.878.853.25 |     | 1<br>1<br>1<br>1<br>1<br>1<br>0.75<br>0.75<br>0.5<br>6 |                  |                  |                  | <b>0</b><br>5 10 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------|------------------|------------------|------------------|------------------|

| Technology (nm) 40 65 7 40   Code CA-Polar/CRC<br>(Universal) CA-Polar<br>(Universal) BCH<br>(Universal) Polar   Algorithm ORBGRAND ORBGRAND ORBGRAND SCL   Code Length Up to 256 128 127 Up to 1024   Supply (V) 1.0 0.9 0.5 0.9   Quantization (bits) 6 5 N.R. 6   Frequency (MHz) 90 454 616 430   Core Area (mm <sup>2</sup> ) 0.4 2.25 5.16 0.64   Target FER 10 <sup>-7</sup> 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW) 4.9 133 277.6 42.8   Energy per bit (pJ/bit) 0.76 2.57 3.52 13.2   Latency (ns) 40.0 2.47 40.6 N.R.                        | 201 | Reference                                              | [1]              | [2]              | [3]              | [4]              |

| Code CA-Polar/CRC<br>(Universal) CA-Polar<br>(Universal) BCH<br>(Universal) Polar   Algorithm ORBGRAND ORBGRAND ORBGRAND SCL   Code Length Up to 256 128 127 Up to 1024   Supply (V) 1.0 0.9 0.5 0.9   Quantization (bits) 6 5 N.R. 6   Frequency (MHz) 90 454 616 430   Core Area (mm <sup>2</sup> ) 0.4 2.25 5.16 0.64   Target FER 10 <sup>-7</sup> 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW) 4.9 133 277.6 42.8   Energy per bit (pJ/bit) 0.76 2.57 3.52 13.2   Latency (ns) 40.0 2.47 40.6 N.R.                                                     |     | Sythesis/Fabricated                                    | Fabricated       | Synthesis        | Synthesis        | Fabricated       |

| Code (Universal) (Universal) (Universal) Polar   Algorithm ORBGRAND ORBGRAND ORBGRAND SCL   Code Length Up to 256 128 127 Up to 1024   Supply (V) 1.0 0.9 0.5 0.9   Quantization (bits) 6 5 N.R. 6   Frequency (MHz) 90 454 616 430   Core Area (mm <sup>2</sup> ) 0.4 2.25 5.16 0.64   Target FER 10 <sup>-7</sup> 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW) 4.9 133 277.6 42.8   Energy per bit (pJ/bit) 0.76 2.57 3.52 13.2   Latency (ns) 40.0 2.47 40.6 N.R.                                                                                        |     | Technology (nm)                                        | 40               | 65               | 7                | 40               |

| Code Length Up to 256 128 127 Up to 1024   Supply (V) 1.0 0.9 0.5 0.9   Quantization (bits) 6 5 N.R. 6   Frequency (MHz) 90 454 616 430   Core Area (mm <sup>2</sup> ) 0.4 2.25 5.16 0.64   Target FER 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW) 4.9 133 277.6 42.8   Energy per bit (pJ/bit) 0.76 2.57 3.52 13.2   Latency (ns) 40.0 2.47 40.6 N.R.                                                                                                                                                                                                     |     | Code                                                   |                  |                  |                  | Polar            |

| Supply (V) 1.0 0.9 0.5 0.9   Quantization (bits) 6 5 N.R. 6   Frequency (MHz) 90 454 616 430   Core Area (mm <sup>2</sup> ) 0.4 2.25 5.16 0.64   Target FER 10 <sup>-7</sup> 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW) 4.9 133 277.6 42.8   Energy per bit (pJ/bit) 0.76 2.57 3.52 13.2   Latency (ns) 40.0 2.47 40.6 N.R.                                                                                                                                                                                                                               |     | Algorithm                                              | ORBGRAND         | ORBGRAND         | ORBGRAND         | SCL              |

| Quantization (bits) 6 5 N.R. 6   Frequency (MHz) 90 454 616 430   Core Area (mm <sup>2</sup> ) 0.4 2.25 5.16 0.64   Target FER 10 <sup>-7</sup> 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW) 4.9 133 277.6 42.8   Energy per bit (pJ/bit) 0.76 2.57 3.52 13.2   Latency (ns) 40.0 2.47 40.6 N.R.                                                                                                                                                                                                                                                            |     | Code Length                                            | Up to 256        | 128              | 127              | Up to 1024       |

| Frequency (MHz)90454616430Core Area (mm²)0.42.255.160.64Target FER10 <sup>-7</sup> 10 <sup>-7</sup> 10 <sup>-6</sup> 10 <sup>-5</sup> Power (mW)4.9133277.642.8Energy per bit (pJ/bit)0.762.573.5213.2Latency (ns)40.02.4740.6N.R.                                                                                                                                                                                                                                                                                                                                           |     | Supply (V)                                             | 1.0              | 0.9              | 0.5              | 0.9              |

| Core Area (mm²)0.42.255.160.64Target FER10-710-710-610-5Power (mW)4.9133277.642.8Energy per bit (pJ/bit)0.762.573.5213.2Latency (ns)40.02.4740.6N.R.                                                                                                                                                                                                                                                                                                                                                                                                                         |     | Quantization (bits)                                    | 6                | 5                | N.R.             | 6                |

| Target FER10-710-710-610-5Power (mW)4.9133277.642.8Energy per bit (pJ/bit)0.762.573.5213.2Latency (ns)40.02.4740.6N.R.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | Frequency (MHz)                                        | 90               | 454              | 616              | 430              |

| Power (mW)4.9133277.642.8Energy per bit (pJ/bit)0.762.573.5213.2Latency (ns)40.02.4740.6N.R.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | Core Area (mm <sup>2</sup> )                           | 0.4              | 2.25             | 5.16             | 0.64             |

| Energy per bit (pJ/bit) 0.76 2.57 3.52 13.2   Latency (ns) 40.0 2.47 40.6 N.R.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | Target FER                                             | 10 <sup>-7</sup> | 10 <sup>-7</sup> | 10 <sup>-6</sup> | 10 <sup>-5</sup> |

| Latency (ns) 40.0 2.47 40.6 N.R.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | Power (mW)                                             | 4.9              | 133              | 277.6            | 42.8             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | Energy per bit (pJ/bit)                                | 0.76             | 2.57             | 3.52             | 13.2             |

| Throughput (Gbps) 6.5 51.8 78.85 3.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | Latency (ns)                                           | 40.0             | 2.47             | 40.6             | N.R.             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | Throughput (Gbps)                                      | 6.5              | 51.8             | 78.85            | 3.25             |

• K. R. Duffy, Invited Speaker, "Universal soft detection decoding in channels with memory - ORBGRAND-Al", Coding Theory for Modern Applications, Joint Mathematics Meetings, San Francisco, January 2024

#### Acknowledgments

This work was partially supported by Defense Advanced Research Projects Agency Contract number HR00112120008 and by National Science Foundation ECCS Award numbers 2128517 and 2128555.

#### References

- [1] A. Riaz et al., "A Sub-0.8pJ/b 16.3Gbps/mm2 Universal Soft-Detection Decoder Using ORBGRAND in 40nm CMOS," in IEEE ISSCC, 2023

- [2] S. M. Abbas et al., "High-Throughput and Energy-Efficient VLSI Architecture for Ordered Reliability Bits GRAND," IEEE TVLSI Systems, 2022

[3] C. Condo, "A Fixed Latency ORBGRAND Decoder Architecture With LUT-Aided Error-Pattern Scheduling," IEEE Transactions on Circuits and Systems, 2022

[4] Y. Tao, et al., "A Configurable Successive-Cancellation List Polar Decoder Using Split-Tree Architecture," IEEE JSSCC, 2021 [5] K. R. Duffy et al., "Ordered Reliability Bits Guessing Random Additive Noise Decoding," IEEE Transactions on Signal Processing, 2022

[6] F. Ercan et al., "GRAND-EDGE: A Universal, Jamming-Resilient Algorithm with Error-and-Erasure Decoding," IEEE ICC, 2023 [7] D. Kam, et al., "A 1.1µs 1.56Gb/s/mm2 Cost-Efficient Large-List SCL Polar Decoder Using Fully-Reusable LLR Buffers in 28nm CMOS Technology," IEEE Symposium on VLSI Technology and Circuits, 2022.

[8] C. -F. Teng, et al., "An Ultra-Low Latency 7.8–13.6 pJ/b Reconfigurable Neural Network-Assisted Polar Decoder with Multi-Code Length Support," IEEE Symposium on VLSI Circuits, 2020.